# ATLAS実験RUN2に向けた レベル1ミューオントリガーへの 新しいアルゴリズムの導入

神戸大学 理学研究科 来見田 吏恵

蔵重久弥,稲丸由夫輝,長谷川誠,佐々木修 $^A$ 石野雅也 $^B$ ,田代拓也 $^B$ ,救仁郷拓人 $^B$ ,鈴木友 $^C$ ,他ATLAS日本TGCグループ $^B$ 、終研大 $^C$

#### Contents

- ➤ LHC RUN2 (2015~)

- ATLASミューオントリガーシステム

(参考:物理学会2012秋季大会 京都大 田代拓也氏による報告)

➤ RUN1でのノイズバースト問題報告、その対処法・実装

#### Motivation for RUN2

| <ul><li>LHC parameter</li></ul> | RUN1 (~2012)         | RUN2 (2015~)         |

|---------------------------------|----------------------|----------------------|

| 重心系energy [TeV]                 | 7~8                  | 13~14                |

| Luminosity $[cm^{-2}s^{-1}]$    | $0.7 \times 10^{34}$ | $1.5 \times 10^{34}$ |

| バンチ間隔 [ns]                      | 50                   | 25                   |

#### • ATLAS LVL1 muon trigger

| $p_T$ threshold | [GeV] | 15  | 20                    |

|-----------------|-------|-----|-----------------------|

| Trigger rate    | [kHz] | 6 ■ | <b>⇒ 34</b> (RUN1の条件) |

RUN1のトリガー条件では、許容トリガーレート(25kHz)を超える可能性あり

#### 物理解析からの要請

ヒッグス粒子の性質測定のために、weakボゾンの崩壊による ミューオンを捉えたい  $\longrightarrow p_T$  threshold 20GeVを維持したい

$p_T$  thresholdは維持、トリガーレートを削減する

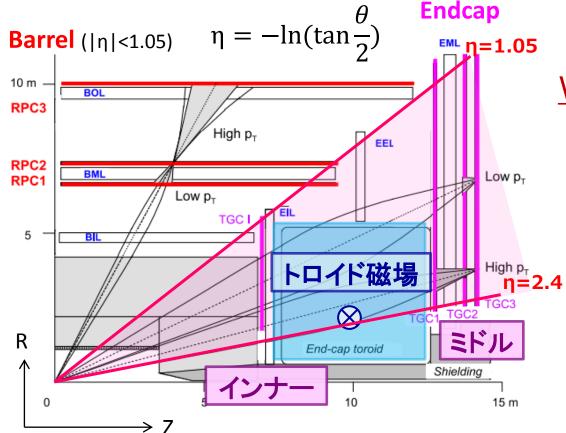

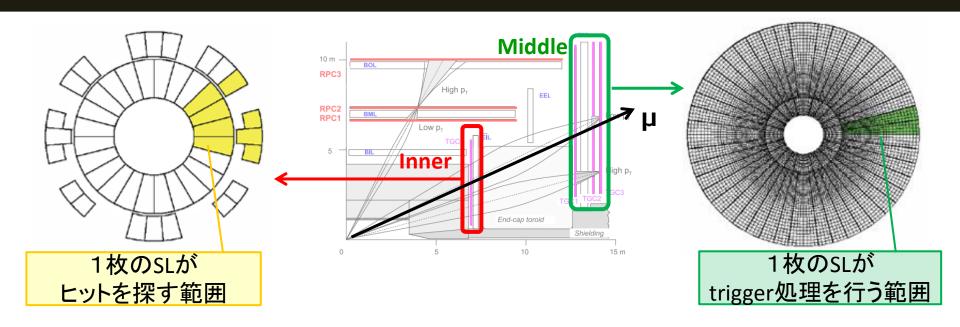

### ミューオントリガー用検出器

**TGC** (Thin Gap Chamber)  $1.05 < |\eta| < 2.4$

外側 3 層(ミドルステーション) 内側 1 層(インナーステーション)

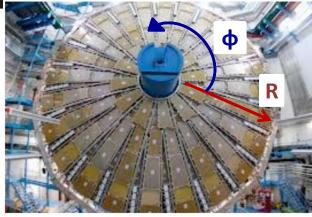

ミドルステーションTGC

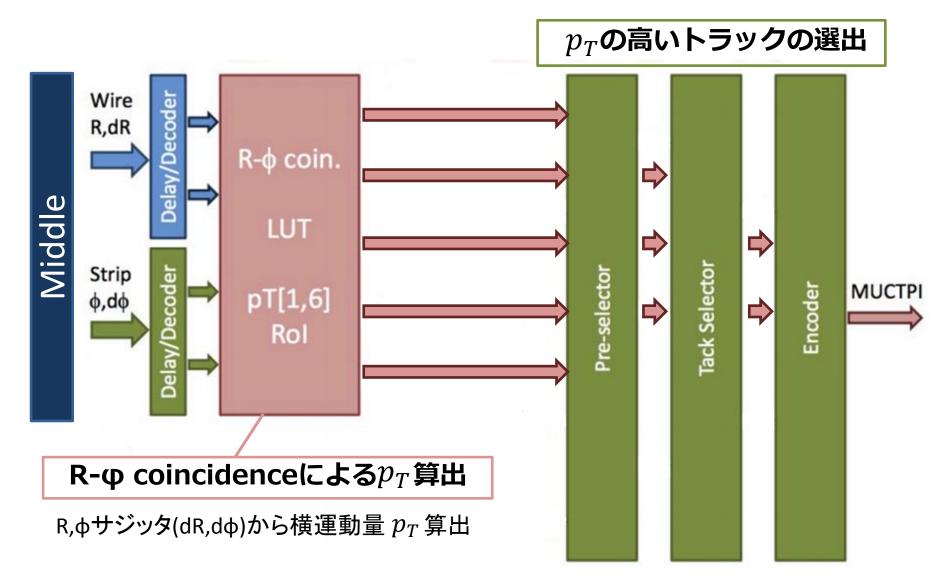

Wire(R方向),strip(φ方向) 2次元読み出し

- ミドルステーションで ミューオンの飛跡を測り、 横運動量( $p_T$ )を算出

- 高い*p<sub>T</sub> の*ミューオンに対し てtriggerを出力

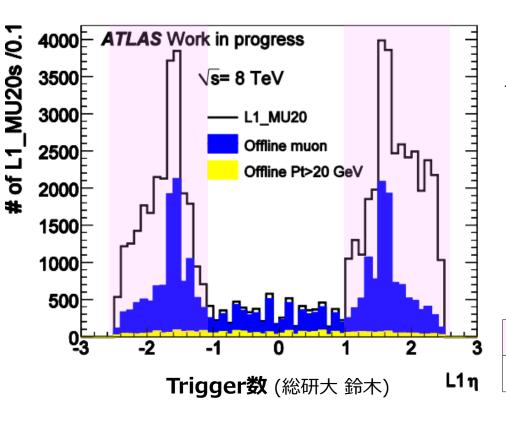

# フェイクトリガー

<u>L1\_MU20</u>:レベル1で20GeV以上と 判断されたイベント

Offline muon (42/100)

Endcap領域 1.05|η|<2.4 Barrel領域 |η|<1.05

Endcap領域において、

衝突点由来のミューオンでない粒子によるトリガー (**フェイクトリガー**)が多く発行されている

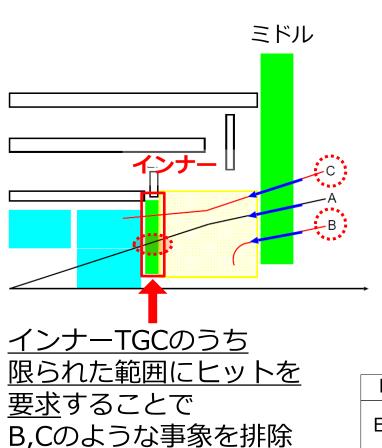

### フェイクトリガー削減方法

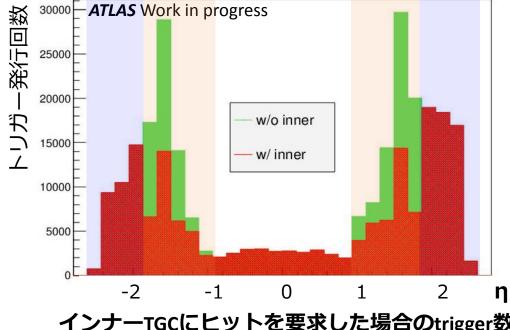

インナーTGCにヒットを要求した場合のtrigger数 (神戸大 稲丸)

| Barrel | RPC  η <1.05                           |

|--------|----------------------------------------|

| Endcap | インナーTGCがカバー <b>する</b> 範囲 1.05< η <1.92 |

|        | インナーTGCがカバー <b>しない</b> 範囲 1.92< n <2.4 |

インナーステーションTGCにヒットを要求することで約30%のトリガーレート削減が可能

フェイクトリガーの起源となる粒子はミドルの直前に位置するトロイド磁石付近や ビームパイプを囲むシールド付近で発生した遅い陽子であるという理解をしている.

#### 実装方法

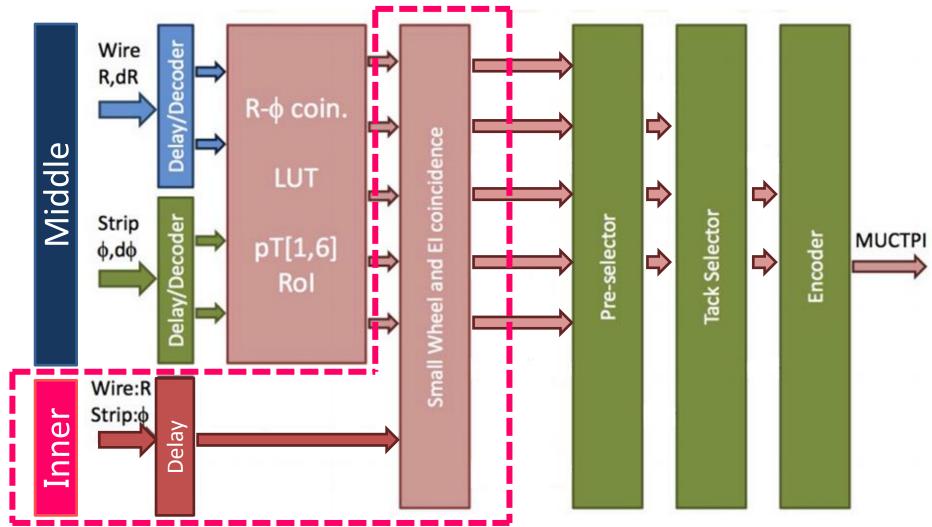

- SL (Sector Logic)

- TGCのtrigger出力を最終的に決定

- →インナーステーションTGCとの coincidenceを取る回路をRUN2で追加

Sector Logic Board

#### firmware & upgrade.

利点: hardwareはそのままでtrigger Logic変更可能

#### 参考

| 処理範囲      | TGC(片側)24分の1 /board                                               |

|-----------|-------------------------------------------------------------------|

| Main FPGA | Virtex- II XC2V3000-BG728 (2chip/board)                           |

| 入力        | G-link×16 (ミドル101bit×2, インナー64bit)<br>各ケーブルでの伝送速度 640 or 680 Mbps |

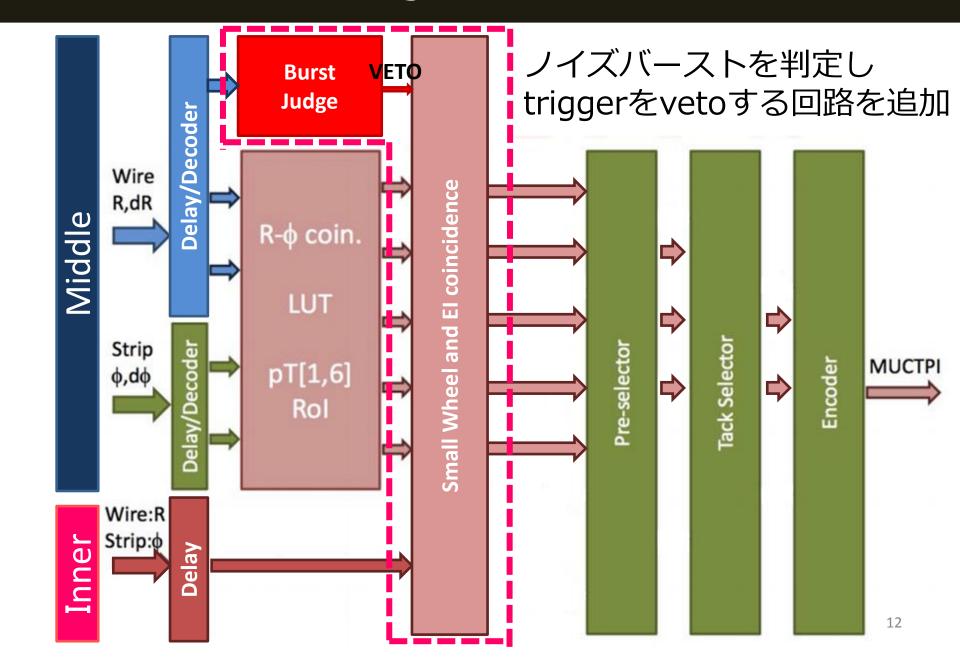

# Block Diagram for RUN1

# Block Diagram for Inner Coincidence

インナーステーションTGCとのcoincidence回路追加

# Inner Coincidence Map

- インナーTGCにhitを要求するのかどうか

- インナーTGCのどこにhitを要求するのか

これらを最適化したInner Coincidence Mapを用いて coincidence処理を行う.

ヒット位置によって異なるMapが必要 ⇒ Block RAMに実装

トリガー効率を維持したままトリガーレートを落とす

#### Noise Burst

RUN1において電気的なノイズが原因と思われるeventが見られた.

このようなeventが 連続して発生し、triggerを発行.

その結果、 データ読み出しバッファの overflowによる障害が生じた.

データ損失を防ぐためには、バッファのoverflowが起こる前に ノイズバーストの兆候を検知する必要がある。

連続したヒット信号を検知しtriggerをvetoする回路を実装 RUN2でSector Logic firmwareに追加.

# Block Diagram for New SL

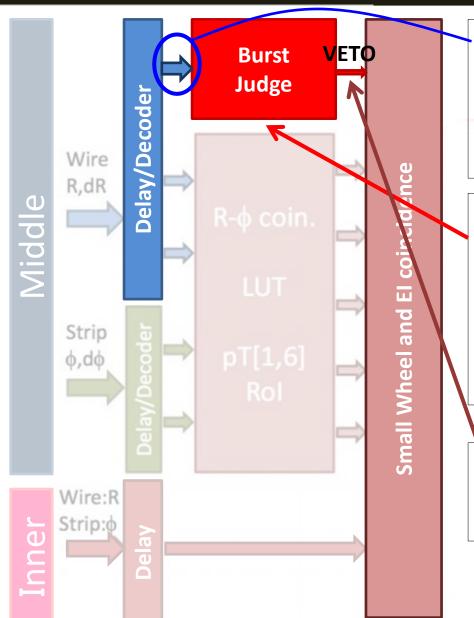

# Scheme for Trigger Veto

R-φ coincidenceを取る前の Wire信号を使用.

- 早期にburstの兆候を捉える

- SLの消費clock数を増やさない

連続したMバンチ中に N回以上trackを検知すると VETO信号を出力.

$M \sim 8$ ,  $N \sim 3$

M,N: Control Registerで指定

VETO信号を受けて triggerを落とす.

### 動作試験①simulation

Simulator: Xilinx社 ISE Simulator

- ✓ Verilog-HDLによるdesign

- ✓ 各機能を個別にsimulation

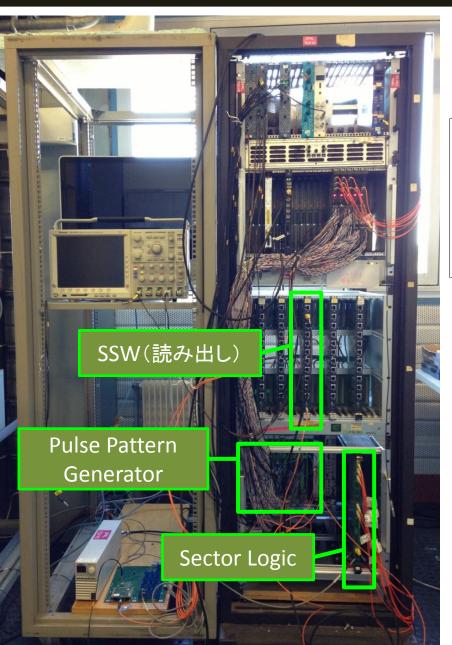

### 動作試験②testbench

新しいfirmwareを実装した SLボードで動作確認を行った.

- ✓ ミドルからの入力101bit, インナーからの入力64bitを再現

- ✓ SLの出力200bitをSSW経由で 読み出し入力信号との整合性を検証

主な機能をチェック

- R-φ Coincidence

- Inner Coincidence

- Burst judge

- Trigger veto

その他SL全体としての動作確認が完了.

SLが設計通りに 動作していることを確認

## Summary

**■ ATLAS実験RUN2に向け、レベル1ミューオントリガーの** 処理を行うSector Logic firmwareの開発を行った

- ✓ インナーステーションTGCを用いたcoincidence回路の実装

- Inner Coincidence Mapを用いてtrigger判定を行う回路の導入により約30%のトリガーレート削減が可能.

- トリガー効率を維持、フェイクトリガーのみを落とす.

- ✓ ノイズバーストの兆候を検知し、TGCのtriggerをvetoする 回路の実装

- 読み出し回路のoverflowを予防し、データ損失を防ぐことが可能.

- レイテンシーは維持したまま新しい回路を実装.

### 今後

- testbenchで実際のInner Coincidence Mapを用いたテストを実施.

- 実機を用いた動作テストを行い、実用化に向けた調整.